[ADC 심화과정] SAR ADC 쉽게 이해하기 (Feat. 축차비교형 ADC 회로)

목차

기초 실무 회로설계 교육

아직도 경력이나 신입의 연차에서 아래와 같은 실무 설계능력이 없다면 꼭 그냥 넘어가시지 말아야 합니다.

기본적인 회로설계능력은 전자 어느 분야를 가도 기본이자 필수입니다.

한번 참고만 해보시기 바랍니다.

📘 ADC 데이터시트를 어떻게 읽어야 할지 막막하셨다면?

📊 실무에서 자주 사용하는 AD9243 vs AD7928을 예시로,

데이터시트를 분석하며 쉽게 이해할 수 있는 유튜브 강의를 준비했습니다!

👉 지금 바로 보러가기 🎥 ADC 데이터시트 분석 강의 시청하기

https://electronic-king.tistory.com/257

[기초 실무 강좌] 회로설계 기초 실무 수강신청자 모집! (Feat. 시험강의 01강, 강의자료 무료 제공)

목차회로설계 연구개발 요구역량기초 실무 회로설계 강의 계획기초 실무 회로설계 강의 00강 오리엔테이션PCB설계교육통신설계교육회로설계 참고사이트안녕하세요. 월간전자연구소 입니다. [

electronic-king.tistory.com

기존 포스팅을 살펴보면 ADC개념과 원리에 대해 설명한 적이 있습니다.

이전 ADC 포스팅이 기본적인 회로설계의 필요한 포스팅이었다면, 오늘은 좀 더 심화과정인 ADC 즉, 아날로그에서 디지털로 변환하는 ADC 변환 방식은 크게 Flash ADC, SAR ADC, Sigma Delta ADC 세 가지가 있는데 오늘은 SAR ADC를 알아보려 합니다.

아직 저희가 사는 세상은 아날로그적인 환경이기 때문에 아날로그로 감지된 정보를 디지털로 가져오기 위해 몇 가지의 디지털 변환 과정을 거쳐야 하는데, 이 과정은 주로 ADC에서 수행합니다.

SAR ADC는 축차 비교형 아날로그 디지털 변환이라고도 하는데요. 자세히 오늘 파헤쳐 보도록 하겠습니다.

이전 ADC포스팅이 궁금하다면 아래 출처 남겨놓았으니 확인해주세요.

SAR ADC란?

아날로그-디지털 변환 회로 방식 중에 축차 비교형 아날로그-디지털 변환 회로(Successive Approximation ADC)는 이진 탐색 방식으로 양자화하는 변환 방식이다.

내부에 DAC와 비교기를 사용하여, 각각의 비트에 대해 한 클럭에 상위(MSB)부터 LSB 쪽으로 결정해가는 방식이다.

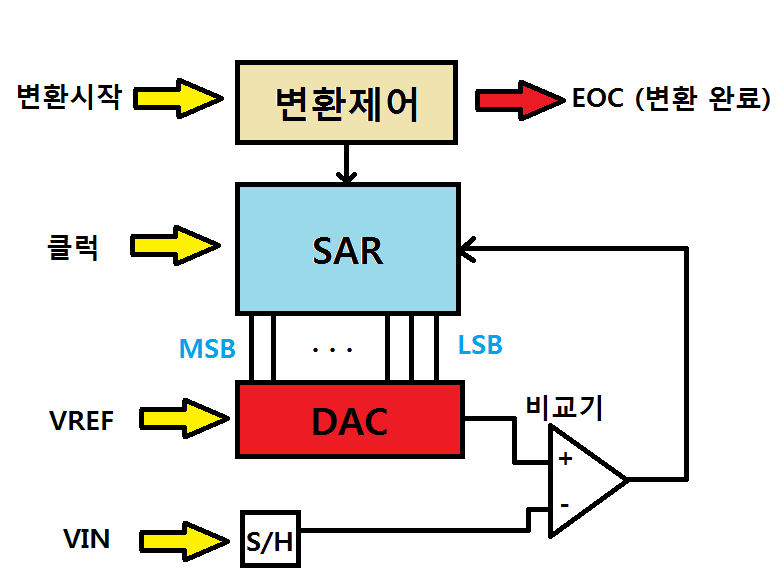

기능도

변환 방법을 살펴보기 전 우선 용어부터 알고 가도록 하겠습니다.

- DAC : 디지털-아날로그 변환 회로

- EOC : 변환 완료

- SAR : 축차 비교 레지스터

- S/H : 샘플 및 홀더

- VIN : 입력 전압

- VREF : 기준 전압

변환 방법

레지스터 또는 아날로그 전압(하드웨어)으로 변환 시작에 대한 신호가 전달되면, 제어회로는 상위 비트(MSB)부터 변환을 시작합니다.

우선 설정된 분해능에 따라 DAC는 아날로그 전압으로 변환하고 변환된 아날로그 전압을 VIN(입력 전압)과 비교합니다.

변환 과정 1

우선 SAR을 최상위 비트를 0으로 설정하고 나머지를 1로 설정한다.

| SAR의 초기값 = 0111...1111 (또는 1000...0000) => DAC => VDAC는 VREF/2 근처. |

변환 과정 2

만약 DAC 전압보다 입력 전압이 작다면 기준 전압의 반 이하가 됩니다. 즉, DAC로 변환된 아날로그 전압이 입력 전압과 비교하여 작다면 비교기의 출력이 LOGIC '1'로 출력이 되고 이것을 보고 SAR의 최상위 비트를 0으로 설정하게 됩니다.

최상위 비트는 기준 전압의 절반을 의미합니다. 즉,

- 최상위 비트 1 : 입력 전압이 기준 전압의 반보다 큰 경우. (VIN > VREF/2)

- 최상위 비트 0 : 입력 전압이 기준 전압의 반보다 작은 경우. (VIN < VREF/2)

라는 뜻이 됩니다. 따라서 비교기의 결과에 따라 최상위 비트를 결정하면 됩니다.

이 과정은 한 클럭의 펄스 동안 결정이 됩니다. 따라서 DAC속도와 비교기의 속도보다 한 클럭의 주기가 빠르면 문제가 되기 때문에 한 클럭의 주기를 고려해야 합니다.

| 클럭의 주기 > DAC 변환시간 + 비교기 전파시간 + SAR논리회로 전파시간 + 안정적 DELAY |

만약 VREF = 10이고 입력 전압 VIN = 3이면 최상위 비트는 0인 것이 됩니다. (아래 예시에서도 적용)

변환 과정 3

최상위 비트가 0으로 결정되면 다음 비트를 결정합니다.

| 0 0 1 1 . . . 1 1 1 1 |

다음 비트는 다시 1/2의 분해능으로 결정합니다. 전체의 1/4로 다시 0과 1을 결정하며, 다시 3V는 2.5V보다 크므로 다음 비트는 1로 설정됩니다.

| 5 > 3 >= 2.5 |

그다음 과정의 비트는

| 0 1 0 1 . . . 1 1 1 1 |

이런 과정 들을 반복하며 전체 비트수만큼 클럭을 진행하면 모든 비트를 결정하게 됩니다.

마지막 비트까지 결정이 되면 EOC에 신호를 설정하여 외부에 변환되었음을 알려주며 SAR ADC 과정이 마무리가 됩니다.

SAR ADC의 장단점

장점

- 구조가 간단하다. 단순히 기준값을 변화하며 반복 비교하는 방식.

- 정확도가 다른 ADC의 비해 정확하다. (여러 번 반복하는 시간만 보장된다면 정확도가 높다)

단점

- 샘플링 속도가 느리다. 비교하고 판단해야 하기 때문에 비교하는 개수가 많아지면 속도가 느려집니다.

- 비교기의 숫자가 늘어날수록 비용 부담이 커진다.

오늘은 SAR ADC에 대해 알아보았습니다.

단순히 생각했던 ADC에도 여러 방식들이 있고, 회로와 사용하는 환경에 따라 사용해야 하는 칩과 구현 방식들이 다양하기 때문에 이런 동작 내용들도 알고 있다면 많은 도움이 되리라 생각합니다. 끝.

'하드웨어 설계 > 실무회로설계' 카테고리의 다른 글

| [기초 실무 강좌] 회로설계 기초 실무 수강신청자 모집! (Feat. 시험강의 01강, 강의자료 무료 제공) (967) | 2021.06.04 |

|---|---|

| [ADC 심화과정] Sigma Delta ADC 쉽게 이해하기 (Feat. 델타시그마 변조) (2) | 2020.11.22 |

| [회로설계 - 기초] EEPROM 이란? (Feat. program code를 이용한 직렬통신) (4) | 2020.09.30 |

| [회로설계 - 기초] EEPROM 이란? (EEPROM 쉽게 이해하기) (0) | 2020.09.06 |

| [회로설계에 필요한 기초 IC 분석] 8. RS422 IC (AM26LV32EID) RECEIVER (2) | 2020.08.30 |