[PADS - 기초] 4. FPGA Logic 설계 (FPGA LOGIC 쉽게 제작하기)

오늘은 프로그래밍 칩인 FPGA 칩을 제작을 해보겠다.

회로설계 시 FPGA를 사용하려면 우선 부품 제작부터 해야 하는데, 보통 핀이 적게는 100 pin, 많게는 676 pin까지 있고 BGA 타입이라 다들 어떻게 해야 할지 난해 할 것이다.

Pin name은 몇백 핀을 하나하나 다 써넣어줘야 하는데, Pin number도 하나하나 다 써넣어야 하는지 이런 고민을 할 텐데 이번 포스팅에서 그러한 난해함을 싹 없애주겠다.

단, 10~20분이면 FPGA Logic 설계가 끝날 것이다. 추후에는 Decal도 생성할 건데 Decal은 5분도 안 걸린다.

잘 따라오길 바란다.

1. Xilnx 홈페이지 접속

검색창에 사용할 FPGA 시리즈명을 입력 후 Pin out을 써준후 검색을 한다.

Download Zip을 클릭하여 다운로드하여준다. 다운로드를 하여 압축을 풀면 파일들이 나오는데, 그중 사용할 FPGA 시리즈를 선택하여 액셀파일을 열어준다. 나는 XC7 S50-CSGA324를 예로 작성하겠다.

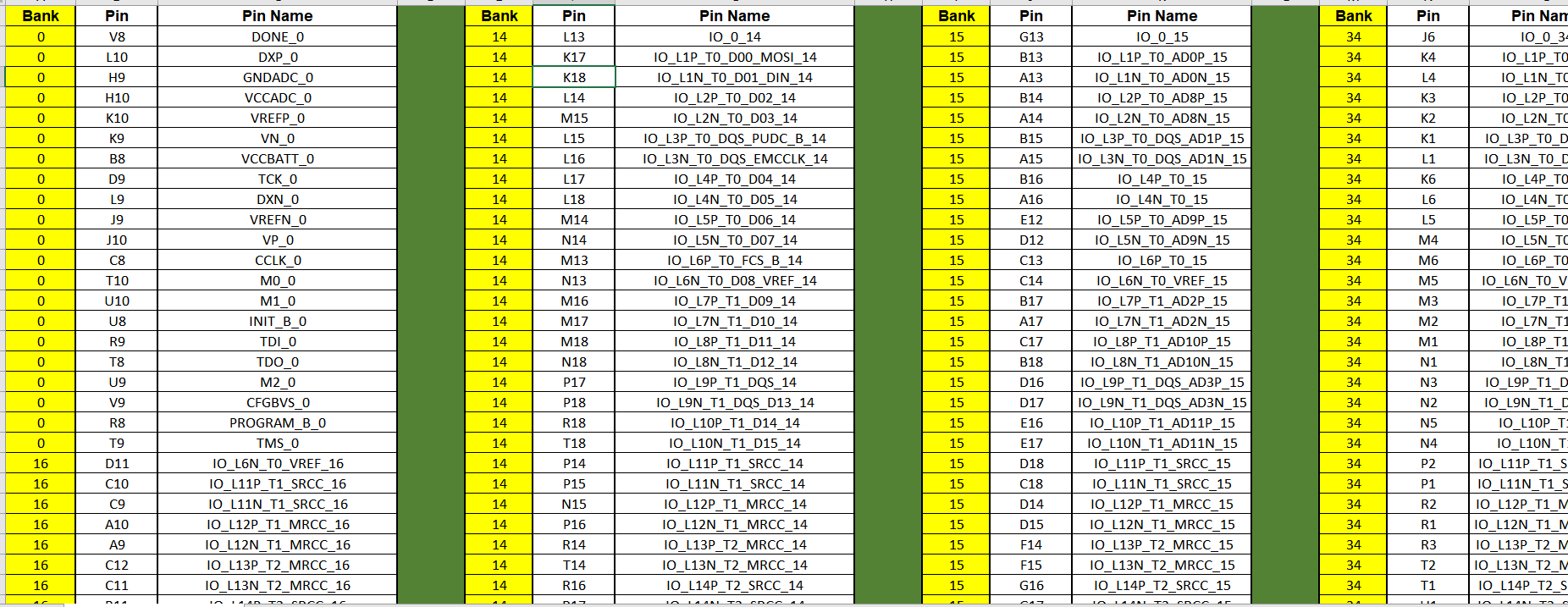

2. 핀 내용에 대한 액셀 파일 정리

처음 액셀파일을 열면 정리가 전혀 안된 내용이 나열되어있다. 실제 FPGA 만들 때 필요한 내용은 BANK와 PIN NAME, PIN NUMBER만 필요하므로 나머지는 모두 아래와 같이 정리해준다.

위의 사진을 보면 BANK가 0, 14 그 외 15, 16 등 나눠져 있는데, 정리는 본인이 편한 대로 하면 되지만 나는 뱅크 별로 나누고 전원별로 나누어 준다.

그렇게 나누면 CONFIGURATION에 사용되는 핀들을 좀 더 쉽게 정리할 수 있으며 전원 관련 핀들도 한 곳에 모여있어 파악하기 쉽다.

위의 예시로 참고하고 정리해두자. 모든 정리가 끝났으면 이제 PADS Logic - Part Editor로 들어가 부품을 생성할 준비를 하자.

3. 부품 제작

FPGA 부품 제작은 다른 부품과는 방법이 상이한 점이 있다. 우선 GATE 가 여러 개가 필요하기 때문에 미리 GATE의 개수를 설정해주고 GATE당 PIN 수에 맞게 터미널을 설계 시 생성해주어야 한다.

(여기서 GATE는 보통 BANK별로 정리하였던 개수대로 설정하는 것이다.)

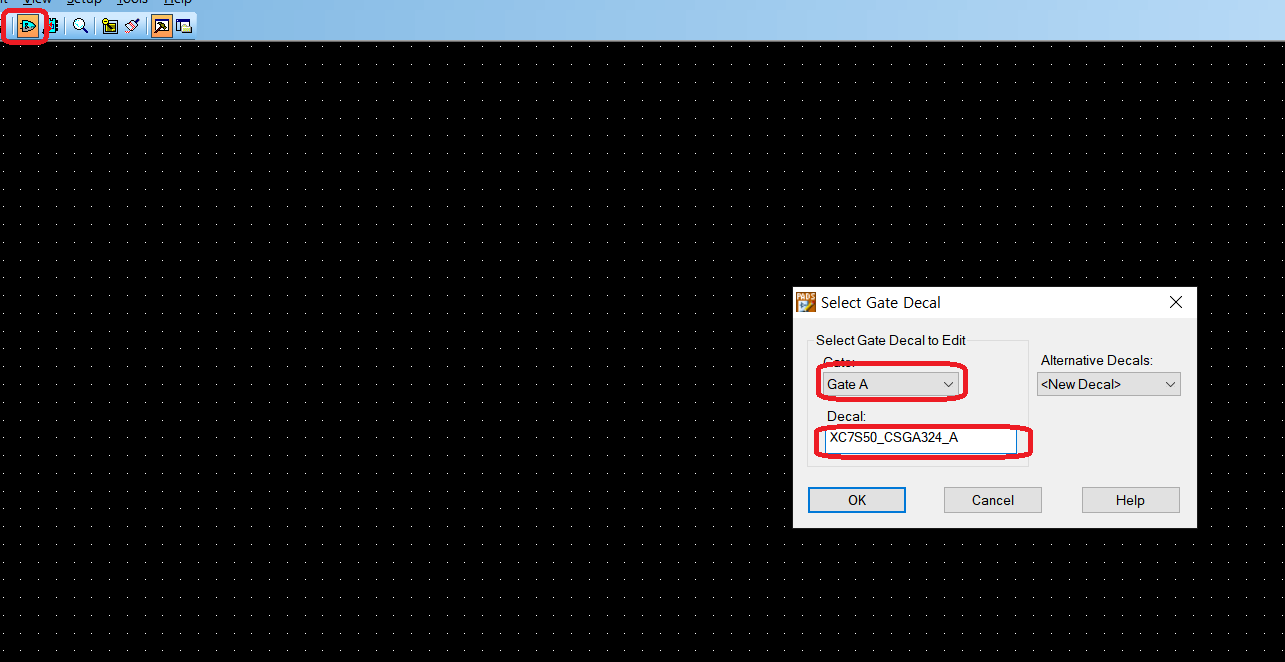

GATE를 개수에 맞게 설정해 주었으면 이제 GATE하나하나 들어가서 만들어 보도록 하겠다.

GATE를 선택하고 이름을 적어준다. OK를 누르면 설계 창이 나온다.

자 이제 여기서부터가 중요하다.

도구 창에 보면 CAE Decal Wizard 아이콘이 있다. 선택해주자.

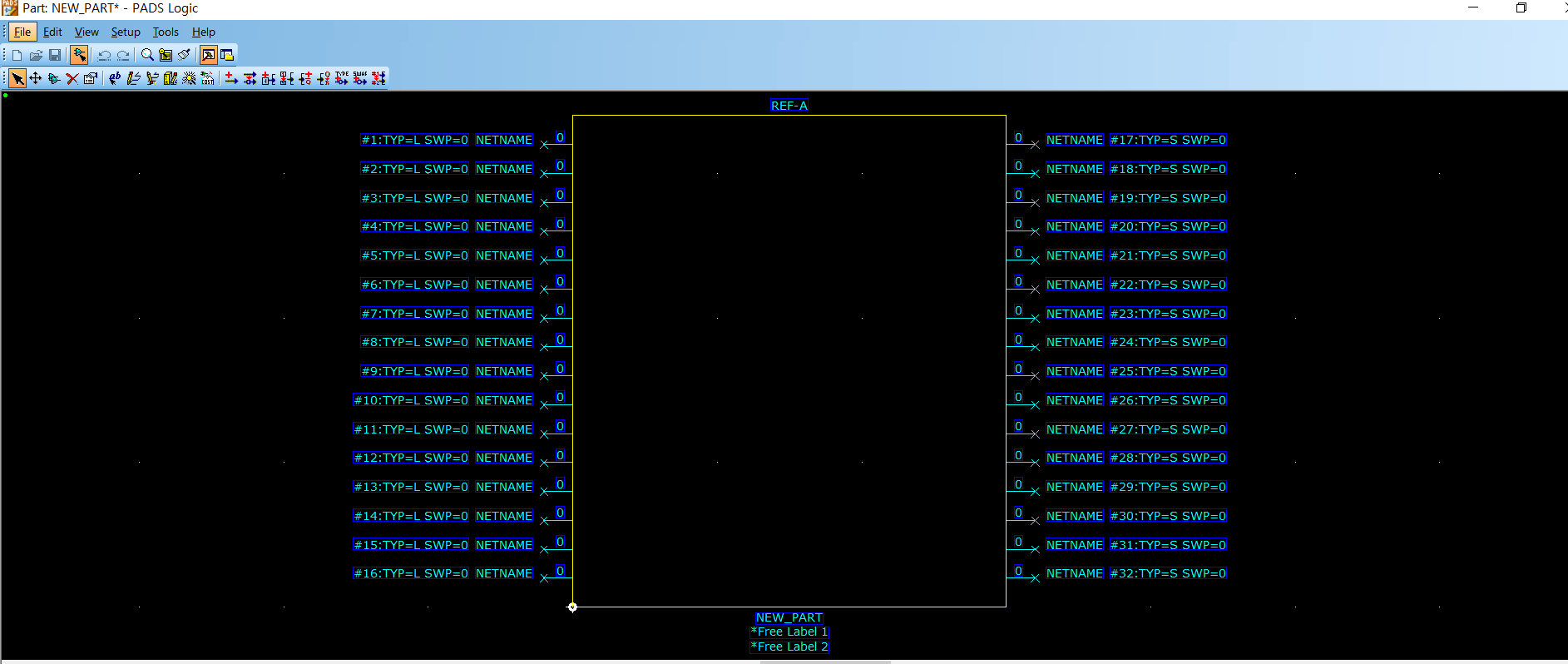

선택하면 작업창이 나오는데 가장 왼쪽에 있는 width, height 등 너비와 높이 등을 크기로 정해준다.

그 옆의 창에서는 왼쪽과 오른쪽에 나타낼 핀의 개수를 설정해주면 수십 핀, 수백 핀의 해당하는 Logic을 바로 생성할 수 있다.

미리 보기 창도 볼 수 있어 용이하다. 이것을 이용하여 수백 핀을 가진 FPGA를 몇 분 만에 뚝딱 할 수 있는 것이다.

이렇게 GATE A에 대한 LOGIC생성이 되었다. 이 내용을 반복하여 GATE A~G까지 생성해준다.

GATE당 핀의 개수가 몇 개인지는 아까 정리해둔 액셀파일을 참고하여 설계해주자.

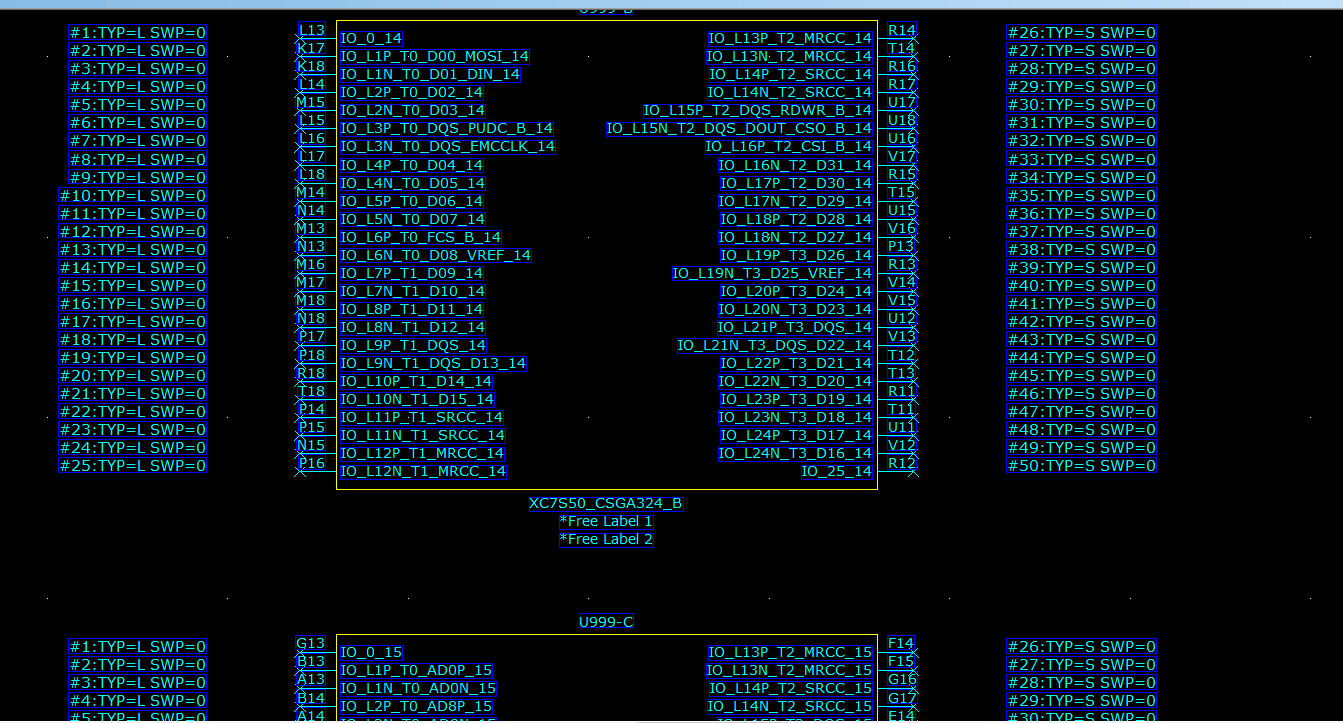

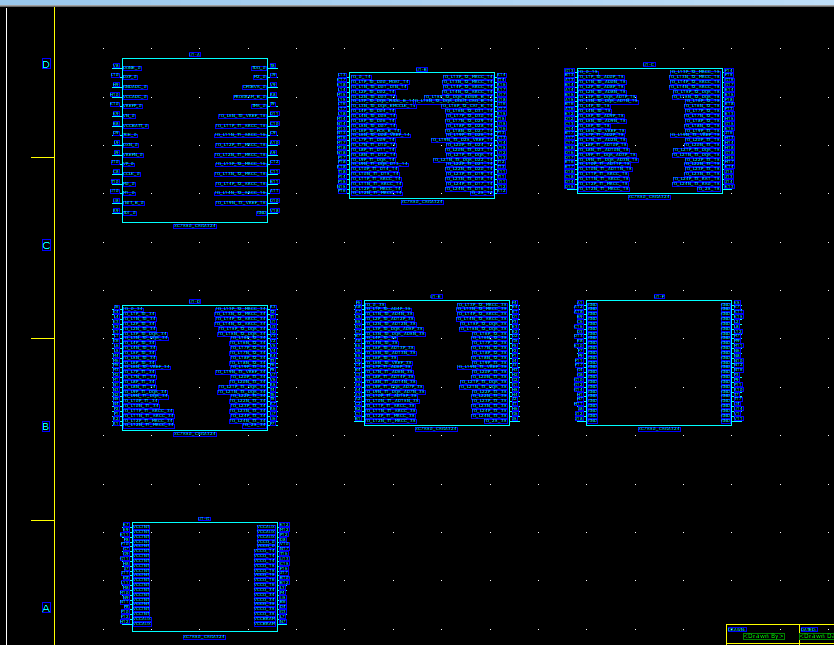

위 그림과 같이 A ~ G까지 다 만들어준 모습이다.

LOGIC은 만들었는데 가장 중요한 PIN NAME과 PIN NUMBER를 아직 할당을 해주지 못했다.

근데 너무 많은 핀들의 이름을 하나하나 치고 써줘야 할까? 분명 좋은 방법이 있을 것이라 생각할 것이다.

바로 우리가 정리해둔 액셀파일에서 단순히 Ctrl + C, Ctrl + V 하면 된다.

아래 내용을 잘 따라오면 된다.

그림과 같이 들어오면 GATE가 설정되어있고, 핀의 넘버와 이름이 비어있는 것을 볼 수 있는데, 해당 빈칸에 복사 붙여 넣기만 하면 된다.

아래의 액셀파일의 내용을 그대로 복사 붙여 넣기 해서 계속 이어주면 된다.

이렇게 모든 핀에 숫자와 이름을 할당하였으면 OK를 누르고 빠져나오자.

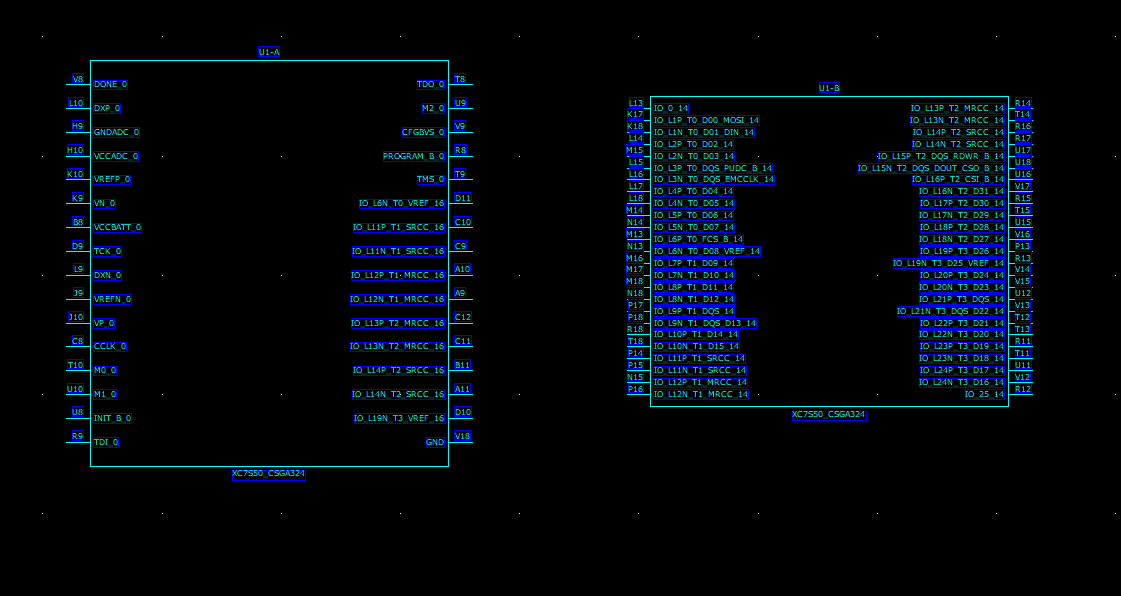

그러면 아래 그림과 같이 내용들이 삽입된 것을 볼 수 있다.

이제 저장만 하면 부품 제작은 끝이다.

4. 회로설계의 부품 적용

이제 만든 부품을 불러와 잘 만들어졌는지, 크기는 적당한지 확인해보도록 하겠다.

이렇게 그림과 같이 잘 나오고 크기도 적당하다면 알맞게 설계한 것이다.

즉, 핀의 개수가 열개든 백개든 Logic에서 어떻게 표현할 것인가는 개발자의 마음이다. FPGA를 제작해보면서 느꼈겠지

만 핀의 개수가 열개여도 GATE를 열개로 나누어서 하든 한 개로 하든 좀 더 회로설계 시 용이할 것 같은 방향으로 편하게 사용하면 된다.

GATE의 개수만큼 해당 부품 파트를 추가하면 계속 연이어 추가가 된다는 점 또한 새로운 내용이다.

다들 오늘의 포스팅을 잘 따라오고 이해가 됐다면 이젠 LOGIC을 통한 부품 제작은 더 이상 어려울 게 없어 보인다.

오늘은 PADS를 이용한 FPGA LOGIC 설계 내용을 다루었다.

많은 도움이 됐길 바란다.

'하드웨어 설계 > [05] PCB 설계 및 제작' 카테고리의 다른 글

| [PADS 9.5 설치 과정] PADS 10분 만에 PADS 설치하기! (245) | 2020.07.12 |

|---|---|

| [PADS - 기초] 5. LAYOUT PCB Decal 제작 하기 (0) | 2020.07.09 |

| [PADS - 기초] 3. LOGIC 부품 제작 & 부품설계(2) (1) | 2020.06.28 |

| [PADS - 기초] 2. LOGIC 부품 제작 & 부품설계(1) (2) | 2020.06.28 |

| [PADS 기초] 1. PADS Tool의 이해(Feat. 입문전 꼭 알아야할 내용 필독!) (2) | 2020.06.28 |